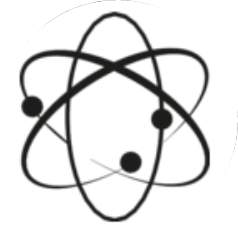

已知一有限状态机系统的状态转移如题30图所示,试用Verilog HDL设计该系统。

说明:

(1)该电路系统有三种状态:S1,S2,S3;

(2)系统具有同步复位功能;

(3)系统输入信号是:

clk:系统时钟

in:lbit位宽的输入数据

rst:bit位宽的同步复位信号,当rst=1时系统状态复位为S1,当rst=0时,系统按照题30图所示的状态转移图工作。

(4)系统输出信号是:

out:1bit位宽的输出数据

(5)状态转移图的图示说明:1/0表示,当输入in=1’b1时,相应输出out=1’b0,以此类推。